**CAE-Tools**

# Neues bei Chip- und Board-Werkzeugen

**Parasitäre Effekte beim Chip-Design zu berücksichtigen, weltumspannend parallel an einem Leiterplattendesign ohne Partitionierung arbeiten zu können oder auch 3D-Leiterplattendesign, alles jüngste Beispiele der Innovationsfreudigkeit in der CAE-Branche.**

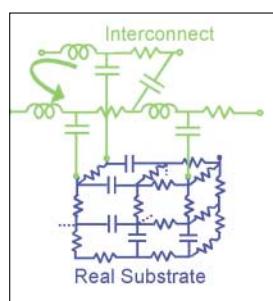

Parasitäre Effekte gehören zu den häufigsten Ursachen für Ausfälle in wireless Designs. Diese Probleme werden im System-IC-Flow und im RF-IC-Flow durch die Cadence Technologie Assura jetzt vollständig berücksichtigt. Die beiden neuen Design-Abläufe zielen dabei auf eine Sender- und Empfangseinheit für WLAN (802.11b) und konzentrieren sich auf das Front-to-Back RF- und Analog/Mixed-Signal-Design. Sie ermöglichen eine gemeinsame Verifikation der HF-, Analog- und Digital-Bereiche im Gesamtsystem. In die Entwicklungsabläufe sind Technologien von Cadence-Partnern integriert. Durch den Cadence Virtuoso AMS-Designer können Entwickler mit Systementwicklungsteams zusammenarbeiten und Bibliotheken der Signal-Processing Workbench (SPW) von CoWare nutzen. Zudem ermöglicht die Verbindung von Matlab/Simulink für einen effizienteren Übergang von der System- auf die IC-Ebene.

In den Flows enthalten sind auch die HF-Design- und Testtechnologien von Agilent – ADS, Momentum und Ptolemy – sowie mit VeloceRF von Helic, eine Entwurfslösung für integrierte Spulen, mit der sich Fehler in den HF-IC-Designzyklen minimieren lassen.

Bild 1: Parasitäre Effekte werden im System-IC- und RF-IC-Designablauf vom Cadence-Assura-Tool jetzt vollständig berücksichtigt.

## Simultanes PCB-Design ohne Partitionierung

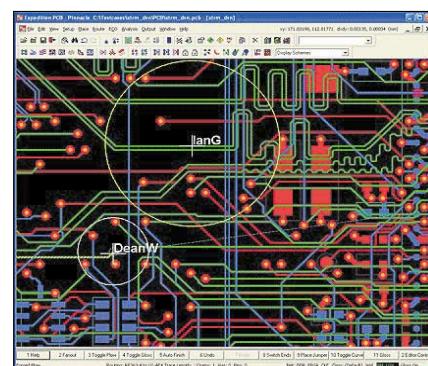

Zwar konnten PCB-Layouter schon länger weltumspannend parallel an einer Leiterplatte arbeiten, aber jeder für sich in einer vordefinierten Partition und ohne in Echtzeit Einsicht in die von anderen Designer vorgenommen Änderungen nehmen zu können. Schon eine einfache Designänderung in einer einzigen Partition, die das ganze Board betreffen könnte, erforderte zuerst ein Zusammenführen des gesamten Designs sowie eine erneute Partitionierung, bevor man weiter arbeiten konnte.

Die XtremePCB-Option von Mentor Graphics eliminiert diese Beschränkungen, da sie jedem die Arbeit am ganzen Board ermöglicht, wodurch eine Partitionierung überflüssig wird. Die XtremePCB Session arbeitet im Hintergrund der Layoutwerkzeuge Mentor Board Station RE oder Expedition. Jeder Leiterplattenentwickler kann eine Design-Session starten oder jederzeit zu einer anderen Session

Bild 2: Wenn ein XtremePCB-Anwender zu einer Session stößt, wird eine Identifikation definiert, der der Cursoranzeige hinzugefügt werden kann, um eine Erkennung des Designers zu ermöglichen.

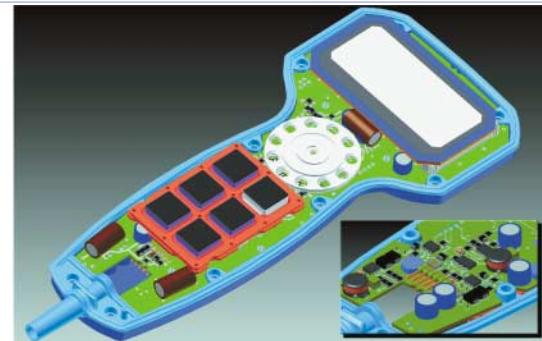

Bild 3: Der Anwender kann mit Cadstar Platinum 3D-Komponenten in der 3D-Umgebung platzieren, verdrehen und austauschen, und gleichzeitig die Design-Prozesse mit direkten Import- und Export-Funktionen vereinfachen.

stoßen. Steigt ein Anwender in eine Session ein, wird der aktuelle Status des Designs automatisch auf dessen Workstation herunter geladen, sodass die kompletten Ressourcen des Geräts genutzt werden können. Die Synchronisation erfolgt automatisch und jedem Entwickler werden alle Modifikationen in Echtzeit angezeigt. Der Session-Server sorgt mit Hilfe von Selektionspriorität und Design Rule Checking dafür, dass Anwender keine Timing-Kollisionen erzeugen oder widersprüchliche Änderungen vornehmen.

## 3D-Leiterplatten-Design

Mit Cadstar Platinum 3D präsentiert Zuken eine Lösung für das Leiterplatten-Design mit 3D-Funktionen. Das Bundle enthält alle Funktionen zur Leiterplattenentwicklung auf einem Desktop-PC und ermöglicht die Zusammenarbeit über MCAD-Standards wie ACIS, STL, SAT, STEP AP203 & AP214. Das Paket vereint Funktionen wie z. B. eine unbegrenzte Anzahl von Komponenten und Layers in einer 3D-Umgebung und bietet u.a. Merkmale wie das Beiseitescielen von Komponenten und Leiterbahnen, die automatische Befüllung einer Fläche mit Kupfer, Leiterbahn-Veränderung, Verbreiterung und selbstkomplettierendes Routing mit Hilfe der 45° Routingalgorithmen.

## KONTAKT

**Cadence** Kennziffer 526

[www.cadence.com/community/virtuoso](http://www.cadence.com/community/virtuoso)

**Mentor Graphics** Kennziffer 527

[www.mentor.com/xtremepcb](http://www.mentor.com/xtremepcb)

**Zuken** Kennziffer 528

[www.cadstarworld.com/platinum3d](http://www.cadstarworld.com/platinum3d)

**AUTOR**

Hans Jaschinski,

Redaktion

*elektronik industrie*

# all-electronics.de

ENTWICKLUNG. FERTIGUNG. AUTOMATISIERUNG

Entdecken Sie weitere interessante

Artikel und News zum Thema auf

all-electronics.de!

Hier klicken & informieren!