## Mixed-Signal Design

# EDA-Tools sollten nicht mehr kosten als ein erfahrener Entwicklungsingenieur

Leider bleiben die Kosten für die Maskenherstellung in einem Markt mit sehr wenig Lieferanten sehr hoch. Den Halbleiterfirmen bleiben für Einsparungsmaßnahmen nur die Kosten der EDA-Werkzeuge oder die Kosten der Entwicklungsingenieure. Allerdings sind die Auswahlmöglichkeiten bei der Digital-Entwicklung ganz anders als beim analogen Design.

Digital-Entwicklungsingenieure können stark von der Automation moderner EDA-Werkzeuge profitieren. Dank Top-Down- und synthesegetriebenen Verfahren wurde die Entwicklung digitaler Chips mit Millionen von Transistoren auch bei einer geringeren Anzahl von Entwicklungsingenieuren erschwinglich. EDA-Werkzeuge wie der Design Compiler von Synopsys oder Silicon Ensemble von Cadence sind teuer, sie sind aber auch entscheidend für den Flow in der digitalen Entwicklung. Dank des hohen, über Hardware-Beschreibungssprachen (Hardware Description Languages – HDL) möglichen Abstraktionsgrades wur-

de eine Entwicklung hoch integrierter ICs ohne den Einsatz von Tausenden von Digital-Entwicklungsingenieuren möglich.

### In der Analogentwicklung ist die Lage ganz anders

In der Analogentwicklung kann man nur sehr selten einen wiederverwendbaren Algorithmus für ein Analog-Design konstruieren, der sich in anderen Schaltungstypen verwenden und zur Automatisierung der Entwicklung einsetzen lässt. Hier kommt es auf die Wahl der richtigen Topologie für die Schaltung an. Diese Auswahl ist stark anwendungsabhängig. Trotz niedriger Transistor-Zahlen in einem Analogdesign ist die Entwicklungsarbeit sehr anspruchsvoll, weil sie ein genaues Verständnis der Beziehungen zwischen den Transistoren und den passiven Bausteinen auf dem Chip erfordert. EDA-Werkzeuge unterstützen daher den Analogentwickler, sie können Ihnen aber nicht ersetzen.

Weil bei der Analogentwicklung keine hochgradige Automatisierung erforderlich ist, müssen effiziente Werkzeuge für die Analogentwicklung nicht teuer sein. Obwohl analoge Werkzeuge die Schaltungsentwicklung nicht direkt automatisieren, gab es Versuche, diesen kundenspezifischen Entwicklungzyklus zu beschleunigen. Manche davon sind nützlich, andere dagegen nicht.

Große EDA-Lieferanten propagieren einheitliche Datenbanken für die verschiedenen Ebenen des Designs, die Vorteile bringen könnten. Allerdings könnte dies dazu führen, dass sich der Entwickler auf unwesentliche Probleme an der Schnittstelle zwischen den analogen und den digitalen Cores konzentriert, wenn es um globale Chip-übergreifende

Probleme handelt, die möglicherweise zum Ausfall einer Schaltung führen können. Leider scheint eine umfassende Chip-Extraktion auf der Ebene der GDSII-Maske immer erforderlich zu sein, wenn man parasitäre Komponenten im Design erfassen möchte. Manche EDA-Hersteller wie z.B. Nassda empfehlen eine Simulation des kompletten Chips. Obwohl die Simulation des gesamten Chips nützlich sein könnte, liefert sie nur eine globale Go/No-Go Information. Die Simulation des gesamten Chips ist als abschließender Funktionstest immer noch sinnvoll, sie verbessert aber nicht den Design-Zyklus. Wichtiger aber ist eine wirksame Spice-Simulation der entscheidenden Funktionsblöcke im Design. Erfreulicherweise müssen effektive Spice-Simulatoren nicht teuer sein. T-Spice Pro von Tanner EDA z. B. ist ein Paket aus einem Spice-Simulator, einem Schaltplan-Editor und einem Wellenform-Viewer für Post-Processing Arbeiten, das insgesamt weniger als 10 000 € kostet.

### Synthetisierbare Analog-IP-Blöcke

Einige neue EDA-Unternehmen werben mit synthetisierbaren Analog-IP-Blöcken. Obwohl diese Lösung anscheinend gut für stark standardisierte Analogblöcke funktioniert, ist sie für die meisten Analogblöcke nicht so effizient. Solche Lösungen sind zudem meist sehr kostspielig. Letztendlich wird die Halbleiter-Entwicklungs-firma eher IP-Elemente kaufen als ein EDA-Tool. Barcelona Technologies bieten komplett kundenspezifische Tapeout-bereite Schaltungen entsprechend detaillierter Anwendungs-Spezifikationen für vordefinierte Analogblöcke. Die Einstellung eines Analog-Entwicklungsingenieurs und der Kauf eines analogen Design-Tools wird den Arbeitgeber wesentlich weniger kosten als der Kauf eines synthetisierbaren

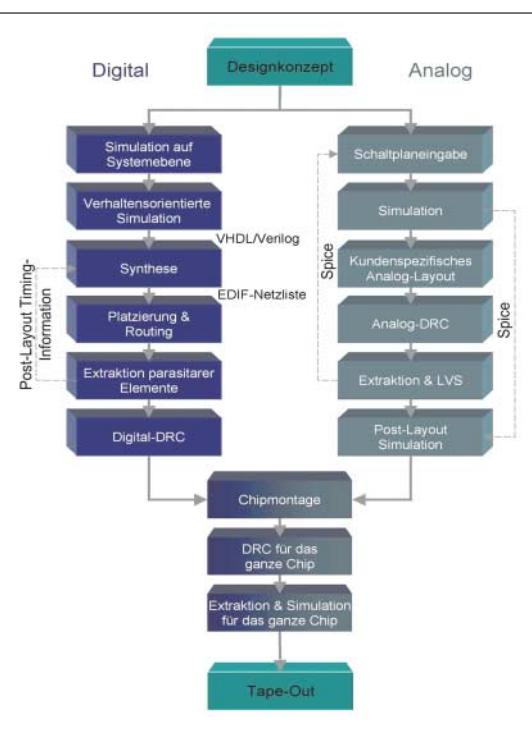

Bild 1: Mixed Signal Design-Ablauf.

| AUTOR | Paul Double ist Geschäftsführer bei EDA Solutions Ltd. |

|-------|--------------------------------------------------------|

|-------|--------------------------------------------------------|

# all-electronics.de

ENTWICKLUNG. FERTIGUNG. AUTOMATISIERUNG

Entdecken Sie weitere interessante Artikel und News zum Thema auf [all-electronics.de!](https://www.all-electronics.de)

**Hier klicken & informieren!**

Analog-IP-Blocks, der Vorteil des IP-Blocks ist allerdings eine kürzere Time-to-Market.

### Mixed-Signal Design

Manche Werkzeuge kommen mit integrierter Unterstützung für eine kunden-spezifische Automatisierung. Mixed-Signal Designer entwickeln oft relativ ähnliche Schaltungen für unterschiedliche ICs oder verschiedene Cores für das gleiche IC, z. B. Phase-Locked Loops zur Ansteuerung unterschiedlicher Digital-Blöcke. Ein wiederholtes Zeichnen dieses Designs mit allen seinen Polygonen ist sehr zeitaufwändig. Glücklicherweise enthalten kostengünstige Tools Skript- und Programmierungsschnittstellen mit ähnlicher Effizienz wie bei High-End Mixed-Signal-Werkzeugen. Viele IC-Entwickler haben zum Beispiel zur Implementation von Funktionsbibliotheken bereits die UPI- und T-Zellen Programmierungsschnittstellen im L-Edit Layoutwerkzeug von Tanner verwendet, um die Arbeit bei der Generierung von Transistoren mit mehreren Finger-Strukturen und anderen komplexen Formen zu automatisieren, die normalerweise beim manuellen Zeichnen viel Zeit benötigen würden.

Diese so genannten T-Zellen sind objekt-orientiert und ermöglichen den Aufbau komplexer Hierarchien aus Schaltungselementen, die sich parametrieren und schnell erzeugen lassen, bevor sie von einem erfahrenen Entwickler angepasst werden.

Die Hersteller anspruchsvoller Mixed-Signal-Werkzeuge machen große Versprechen zu den mit ihren Tools erreichbaren Produktivitätsverbesserungen. Betrachtet man die Funktion eines Mixed-Signal-Designs etwas genauer, ist gar nicht mehr so sicher, ob Funktionen wie z. B. On-the-Fly Design-Rule Checks wirklich so effizient wie versprochen arbeiten. Design-Rule-Überprüfungen sind wichtig, sie werden aber immer komplexer, wenn Foundries die Beziehung zwischen Schaltungs-Layouts und den fertigungstechnischen Besonderheiten von Materialien wie etwa von Low-K-Dielektrika berücksichtigen müssen. Die nötigen Design-Rule Checks zur Sicherung einer hohen Ausbeute erfordern immer häufiger eine globale Analyse, wie sie Back-End Tools wie z. B. Calibre von Mentor Graphics bieten. Zwar können On-the-Fly Design-Rule Checks lokale Probleme aufzeigen, oft aber liefern sie keine Hinweise auf ernstere Regelverletzungen, bei denen es um Chip-übergreifende Effekte geht. Dies stellt folglich ihre Nützlichkeit für den Mixed-Signal-Designer in Frage. Calibre von Mentor Graphics ist als eines der schnellsten erhältlichen DRC-Tools relativ teuer. Erfreulicherweise haben einige EDA-Unternehmen im DRC-Bereich die Standardisierung auf Calibre genutzt und ihrer eigenen Werkzeuge Calibre-kompatibel ausgelegt. So hat Tanner EDA vor kurzem mit HiPer Verify ein Werkzeug vorgestellt, dass ohne Modifikation und mit ausreichender Geschwindigkeit Calibre-Dateien für alle bis auf sehr komplexe analoge und Mixed-Signal-Designs ausführen kann, aber nur einen Bruchteil des Preises ähnlicher Werkzeuge größerer Anbieter kostet. Weil der DRC im Hintergrund läuft, kann der Anwender die Fehler schon während der DRC-Ausführung betrachten und sein Layout weiter editieren, was die geringere Tool-Geschwindigkeit kompensiert. Für Anwender, die mehrere Foundries benutzen, ermöglicht HiPer Verify eine einfache Umstellung von einer Foundry zu anderen, ohne dass dabei jedesmal die DRC-Regeln manuell aktualisiert werden müssen.

(jj)

### KOMPAKT

Die Analogentwicklung lässt sich nicht auf die gleiche Weise wie die Digitalentwicklung automatisieren. Die von den großen EDA-Anbietern propagierten voll-integrierten Design Flows sehen in der Theorie interessant aus. Oft ist aber nur schwer zu erkennen, wie ihre Kosten gerechtfertigt werden können, wenn wesentlich preisgünstigere Werkzeuge von kleineren Spezialanbietern die gleichen Ergebnisse bei vielleicht nur einem Zehntel des Preises bieten und dabei noch kompatibel zu Industriestandards wie GDSII und Calibre sind.

ger eine globale Analyse, wie sie Back-End Tools wie z. B. Calibre von Mentor Graphics bieten. Zwar können On-the-Fly Design-Rule Checks lokale Probleme aufzeigen, oft aber liefern sie keine Hinweise auf ernstere Regelverletzungen, bei denen es um Chip-übergreifende Effekte geht. Dies stellt folglich ihre Nützlichkeit für den Mixed-Signal-Designer in Frage. Calibre von Mentor Graphics ist als eines der schnellsten erhältlichen DRC-Tools relativ teuer. Erfreulicherweise haben einige EDA-Unternehmen im DRC-Bereich die Standardisierung auf Calibre genutzt und ihrer eigenen Werkzeuge Calibre-kompatibel ausgelegt. So hat Tanner EDA vor kurzem mit HiPer Verify ein Werkzeug vorgestellt, dass ohne Modifikation und mit ausreichender Geschwindigkeit Calibre-Dateien für alle bis auf sehr komplexe analoge und Mixed-Signal-Designs ausführen kann, aber nur einen Bruchteil des Preises ähnlicher Werkzeuge größerer Anbieter kostet. Weil der DRC im Hintergrund läuft, kann der Anwender die Fehler schon während der DRC-Ausführung betrachten und sein Layout weiter editieren, was die geringere Tool-Geschwindigkeit kompensiert. Für Anwender, die mehrere Foundries benutzen, ermöglicht HiPer Verify eine einfache Umstellung von einer Foundry zu anderen, ohne dass dabei jedesmal die DRC-Regeln manuell aktualisiert werden müssen.

### KONTAKT

TransEDA Kennziffer 521

[www.transeda.com](http://www.transeda.com)