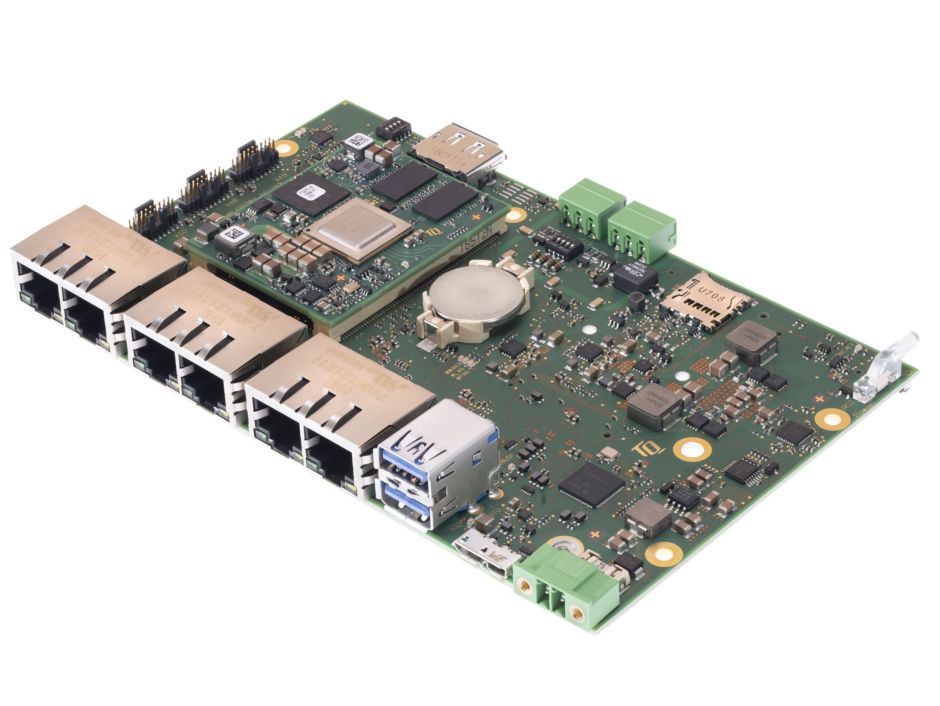

(Bild: TQ-Systems)

Eckdaten

Hinter der QorIQ-Layerscape-Technologie verbergen sich Lösungsmöglichkeiten, die die Herausforderungen einer schnellen Datenkommunikation unter Berücksichtigung eines geringen Energieverbrauchs bewältigen. Hierdurch ergeben sich neue, zukunftsweisende Wege, um jegliche Arten von Daten sicherer und schneller zu übertragen.

NXP (vormals Freescale) veröffentlichte im April 2013 erste Informationen, dass neben der bereits am Markt bekannten und erfolgreichen Power-Architektur eine neue Prozessorgeneration namens Layerscape auf den Markt gebracht wird. Zu diesem Zeitpunkt war noch nicht bekannt, dass die neu konzipierten, auf ARM-Core-basierten CPUs, die Power-Architektur ersetzen sollen.

Mitte 2014 gab NXP bekannt, dass die Roadmap der Power-Architektur nicht mehr weitergeführt und von der QorIQ-Layerscape-Technologie langfristig ersetzt wird. Das erste CPU-Derivat, das 2013 auf den Markt kam, bestand aus drei pin-kompatiblen Varianten der LS1021A. Anfang 2014 folgten dann Informationen zur Roadmap. Ab hier ging es dann Schlag auf Schlag und weitere CPU-Derivate wurden angekündigt. Als zweite CPU kam der LS2088A auf den Markt. Dieser ist jedoch aufgrund seiner speziell auf den Servermarkt ausgerichteten Eigenschaft nicht so stark verbreitet, wie die im Jahr 2015 angekündigten Serien LS1088A, LS1043A und LS1046A. Ende 2018 hat NXP dann den LS1028A angekündigt. Anfang dieses Jahres soll das High-End-CPU-Derivat LX2160A, das mit den schon heute bekannten Features viel Neues im Bereich der Netzwerktechnologie verspricht, auf den Markt kommen.

Hinter dem Namen verbirgt sich die Kombination aus einem energieeffizienten ARM-Core und der High-Speed-Peripherie der QorIQ-Power-Architektur. Die Anbindung des ARM-CPU-Kerns an die Kommunikationseinheit ist mittels eines neuen Bus-Systems „Cache Coherent Interconnect“ (CCI400) realisiert. Diese Kombination bildet eine ideale Plattform für anspruchsvolle Aufgaben im Bereich der Datenübertragung.

Durch die Integration der bekannten QUICC-Engine-Technologie (auch QE genannt) von Freescale können die Layerscape-CPUs bei Nachfolgeprojekten, bei denen diese QE bisher verwendet wurde, weiterhin eingesetzt werden. Ein Vorteil dieser Architektur ist, dass sowohl Big-Endian (angewendet bei der Power-Architektur) und Little-Endian (angewendet bei der allgemeinen ARM-Technologie) bei diesen Layerscape-Prozessoren unterstützt werden. Das bedeutet, dass bisher auf der Power-Architektur angewendete Applikationen und Rechenoperationen, wie auch bisher verwendete Software, einfacher portierbar und angewendet werden können.

Eigenschaften der LS1021A-Familie

Die Embedded-CPU LS1021A mit den Varianten LS1020A und LS1022A ist für Systementwickler optimiert, die hocheffiziente Plattformen auf neuester Systemarchitektur zur Verarbeitung von hohen Datenvolumen entwickeln möchten. Die LS102xA-CPU-Familie bietet einen Dual-Cortex-A7 Core mit ECC-Protection geschützten L1- und L2-Cache für ein Maximum an Zuverlässigkeit. Die durchschnittliche Leistungsaufnahme des Prozessors liegt bei 3 bis 4 W. Mit dem im LS1021A-Prozessor integrierten LCD-Controller lassen sich auch Systementwicklungen realisieren, die Anforderungen an eine Bedieneinheit mit Display und Touch stellen. Dadurch ergibt sich ein großer Kostenvorteil. Anwender können zur Kommunikation neben 3 × Gigabit Ethernet, 2 × PCIe Gen2, USB 2.0-Host / USB 3.0-OTG-Controller und zehn UARTs auch bis zu vier FlexCAN (nur beim LS1021A) nutzen. Weitere Funktionseinheiten können über Sata, SDIO, SPI, I2C und I2S angebunden werden.

Der LS1012A basiert auf der neuen 64-Bit-Cortex-A53-QorIQ-Layerscape-Technologie und eignet sich hervorragend für robuste und industrietaugliche Router, Gateways und kleine Datalogger. Neben einem 16 Bit breiten DDR3L-RAM-Interface, das einen Ausbau bis zu einem GB erlaubt, können Nutzer zusätzlich als Boot Device einen QSPI-NOR-Flash mit einer maximalen Speichergröße von 256 MB nutzen. Eine Verlustleistung von 1 W in Verbindung mit den in der CPU umgesetzten High-Speed-Interfaces versprechen vielfältige Einsatzmöglichkeiten. Es können Applikationen verwirklicht werden, bei denen sowohl ein sehr niedriger Energieverbrauch als auch eine sichere und schnelle Datenkommunikation gefordert ist. Neben 2 × Gigabit-Ethernet, PCIe 2.0, Sata3, USB 3.0 gibt es noch UARTs, I2C als auch I2S, die verwendet werden können.

10-Gigabit-Ethernet mit der LS1043A-/ LS1046A- und LS1088A-Familie

Anwender profitieren von einer sehr leistungsfähigen Plattform zu attraktiven Konditionen. Für verschiedene Anwendungen wie Networking, industrielle Automation und Steuerungen mit hohen Anforderungen an eine schnelle und sichere Datenkommunikation stehen bis zu fünf optimierte CPU-Varianten zur Verfügung. Die pin-kompatiblen CPUs (LS1046A/26A, LS1043A/23A, LS1088A) unterscheiden sich in der Architektur und Anzahl der Cores. Je nach Konfiguration kommen dabei ein Cortex-A72 oder -A53, jeweils mit Dual- oder Quad-Core, oder ein Cortex-A53 mit Octa-Core mit einer Taktrate von bis zu 1,8 GHz zum Einsatz.

Die CPU-Vielfalt ermöglicht je nach Anforderung die Auswahl eines optimalen Verhältnis zwischen hoher CPU-Rechenleistung, schnellen Datenübertragungsraten und Verlustleistung das passende von fünf Derivaten auszuwählen. Zur Hochgeschwindigkeits-Kommunikation können unter Berücksichtigung von bis zu acht SerDES-Lanes, bis zu jeweils 2 × 10-Gigabit-Ethernet, 5 × Gigabit, 3 × PCIe Gen3 und 1 × Sata 3.0 verwendet werden. Zudem werden noch maximal drei USB-3.0-High-Speed-Schnittstellen neben UARTs, I2C und GPIOs angeboten. Als Speicher stehen DDR4-SDRAM mit ECC, ein SDIO und zwei Quad-SPI-Schnittellen zur Verfügung.

TSN und Grafik mit den LS1028A-CPUs

Beim ARM Layerscape LS1028A der NXP-Prozessorfamilie wird auf die Cortex-A72-Technologie gesetzt. Auf Basis dieser CPU kann, je nach benötigter Funktionalität, zwischen vier verschiedenen pin-kompatiblen CPU-Varianten gewählt werden. Die CPUs unterscheiden sich darin, dass es zwei Single-Core-Varianten (LS1017A und LS1018A) alternativ zu den Dual-Core-Varianten (LS1027A und LS1028A) gibt. Bei den beiden CPUs LS1017A und LS1027A wurde die Grafikfunktion deaktiviert. Die integrierte Grafik beim LS1018A und LS1028A unterstützt mit einer leistungsfähigen GPU Displays mit einer Auflösung von bis zu 4K. Mit einer Taktrate von bis zu 1,3 GHz bietet diese CPU-Familie eine umfassende und skalierbare Plattform bei niedriger Verlustleistung.

Für eine schnelle und echtzeitfähige Datenkommunikation steht ein TSN-fähiger Gigabit-Ethernet-Switch mit vier Ports zur Verfügung. Zusätzlich können noch zwei Schnittstellen für Gigabit-Ethernet (1G/2,5G) genutzt werden. Die 2,5-GB-Ethernet-Schnittstelle ist ebenfalls für TSN ausgelegt. Die CPUs verfügen neben UARTs, SDIO, I²C zudem über folgende Schnittstellen: bis zu 2 × PCIe Gen3, 2 × USB 3.0, 1 × Sata 3.0 sowie 2 × CAN. Als Speicher kann DDR4-SDRAM mit bis zu 4 GB inklusive ECC-Support und über SDIO ein eMMC-Speicher realisiert werden. Zusätzlich kann über zwei QSPI-NOR-Flash-Interfaces ein Speicherausbau von bis zu 512 MB umgesetzt werden. Diese CPUs eignen sich besonders im Bereich der industriellen Automation und Steuerung auf TSN-Basis, Networking sowie für Anwendungen mit Bedarf an schneller, echtzeitfähiger und sicherer Datenkommunikation in Verbindung mit Grafik.

Der LX2160A mit 100-Gigabit-Ethernet

Der High-End-Kommunikationsprozessor LX2160A bietet die Möglichkeit 24 High-Speed-SerDES-Lanes mit bis zu 25 GHz für die schnelle Datenkommunikation zu nutzen. Die SerDES-Lanes können für Sata, PCIe, oder Ethernet unter Berücksichtigung des angewandten Pin-Multiplexings eingesetzt werden. Die Rechenleistung lässt sich dank acht, zwölf oder 16 Cortex-A72-Cores umfassend skalieren. Mit dieser CPU von NXP können bis zu zwei 100-Gigabit-Ethernet-Schnittstellen realisiert werden. Zwei 72 Bit breite Speicherinterfaces sorgen für die Möglichkeit, ausreichend DDR4 mit ECC-Unterstützung anzubinden. Neben zwei CAN-FD, acht I2C und SPI wurden zwei USB 3.0 in die CPU integriert. Ebenfalls mit dieser CPU können Anwender ihre Anforderungen für Server, High-End-Kamera-Übertragungen sowie Satellitentechnik im noch nie dagewesenen Umfang realisieren. Für eine geschützte und sichere Datenübertragung kann auf umfangreiche Security-Funktionen zurückgegriffen werden.

Die QorIQ-Layerscape-CPU-Produktgeneration besteht innerhalb jeder Familie wiederum aus pin-kompatiblen CPU-Varianten und kombiniert dadurch zahlreiche Funktionen und Leistungsklassen für zukunftsorientierte Entwicklungen. Je nachdem, welche Anforderungen an das Design gestellt werden, kann ein passender Kern aus der jeweiligen CPU-Familie ausgewählt werden. Somit ist diese CPU-Serie beginnend mit einem Dual-Cortex-A7-Kern bis hin zu 16 Cortex-A72-Kernen die ideale Grundlage für Anwendungen aus verschiedensten Bereichen und Anwendungen, bei denen die zukunftsweisende Netzwerktechnologie ihren Einsatz finden soll.

TQ-Systems hat sich all die CPU-Vorteile zu Nutzen gemacht und darauf basierend das auf dem Markt größte Produktportfolio von Embedded-Modulen entwickelt. Jedes Modul stellt 100 % aller verfügbaren Signalpins bereit, sodass der Anwender keiner Limitierung bei der Verwendung der Schnittstellen und dessen Pin-Multiplexings unterliegt.

(neu)